# Debug Your Embedded Design More Quickly

#### August 19th, 2003

presented by:

#### Mike Beyers Oscilloscopes Project Manager

© Copyright 2003 Agilent Technologies, Inc.

- Trends in Embedded Systems

- SDRAM and PCI Overview

- Turn on Process Recommendations

- "Late in the Game" Debug Process Recommendations

- Recommended Agilent Products

- Additional References

- Trends in Embedded Systems

- SDRAM and PCI Overview

- Turn on Process Recommendations

- "Late in the Game" Debug Process Recommendations

- Recommended Agilent Products

- Additional References

#### **Trends in Embedded Systems - Past**

- 20 Years ago each embedded processor system was a unique design.

- The processor had no internal memory or IO control.

- Therefore memory and IO control was kept relatively simple.

- Digital signals were easily probed with a four channel analog oscilloscope.

#### **Trends in Embedded Systems - Today**

- Today, processors and FPGAs can include complex memory and IO control systems.

- Technologies like SDRAM for memory and PCI for IO have migrated from high-end computers to mid-range embedded systems in only a handful of years.

- The modern embedded system designer will need a variety of tools when debugging these more complex systems.

- Trends in Embedded Systems

- SDRAM and PCI Overview

- Turn on Process Recommendations

- "Late in the Game" Debug Process Recommendations

- Recommended Agilent Products

- Additional References

## **SDRAM Control Signals.**

- Need to view 5 digital signals to identify/trigger on a particular cycle - the three to the right plus chip select and Clock.

- Need to look at least clock and another line (address, data or control) with analog channels to verify timing and signal integrity.

- Operation is pipelined.

#### **SDRAM** Commands

| Command                  | RASN | CASN | WEN |

|--------------------------|------|------|-----|

| No Operation (NOP)       | Н    | Н    | Н   |

| Active (ACT)             | L    | Н    | Н   |

| Read (RD)                | Н    | L    | Н   |

| Write (WR)               | Н    | L    | L   |

| Burst Terminate (BT)     | Н    | Н    | L   |

| Precharge (PCH)          | L    | Н    | L   |

| Autorefresh (ARF)        | L    | L    | Н   |

| Load Mode Register (LMR) | L    | L    | L   |

# **PCI Control Signals.**

- PCI is a very complex protocol. The PCI bus specification is 322 pages!

But it is commonly used and cheap to implement..

- Besides the 4 command lines, there are 6 control lines (FRAME#, TRDY#, IRDY#, STOP#, DEVSEL# and IDSEL), 2 error signals, 2 arbitration signals, and a clock and reset line.

#### PCI Commands

#### C/BE[3:0]# Command Types

- 0000Interrupt Acknowledge0001Special Cycle

- 0010 I/O Read

- 0011 I/O Write

- 0100 Reserved

- 0101 Reserved

- 0110 Memory Read

- 0111 Memory Write

- 1000 Reserved

- 1001 Reserved

1110

- 1010 Configuration Read

- 1011 Configuration Write

- 1100 Memory Read Multiple

- 1101 Dual Address Cycle

- Memory Read Line

- 1111 Memory Write and Invalidate

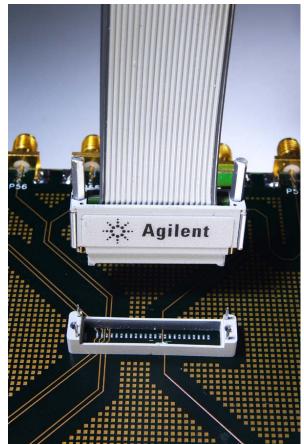

# Hint #1: Add LA Connector Footprints

The user puts down a 'landing pattern' on the target system.

The connector-less probe is then attached to the system with a 'retention module'

- Trends in Embedded Systems

- SDRAM and PCI Overview

- Turn on Process Recommendations

- "Late in the Game" Debug Process Recommendations

- Recommended Agilent Products

- Additional References

#### Hint #2, 3, 4: Start with Raw Board

- Hint #2: Check for ground and power plane shorts with DMM. Check loaded board too!

- Hint #3: Check R across power planes and calculate expected IR loss.

- Hint #4: Check controlled impedance lines with TDR. Concentrate on Clock traces, as they are most sensitive in syncronous systems like SDRAM and PCI.

#### **Loaded Board Turn-On**

### Hint #5: Check Supplies with Scope

- Use Scope instead of DMM see noise and dynamic loading issues. Modern CMOS devices can load down a PS when they come out of reset or do a burst of memory or IO accesses.

- Re-check supplies once everything is working. Power consumption is dependent on operation.

- Check with current probe if supply droops.

#### Hint #6: Check PS Sequencing

- Modern IC's often use several different supply voltages - for core and IO.

- Follow manufacturer's recommendation (On and Off!).

- Consider distributed power with DC-DC conversion off one rail. Soft start options allow control of power supply sequencing.

- Rule of thumb bring all supplies up together if no manufacturer's recommendation.

#### **Next Step - Look for Clocks.**

- Clocks will normally be your highest speed signals.

- Edge rates are probably 1ns or less.

- BW<sub>Signal</sub> ~= 0.5 / risetime.

- Hint #7: BW<sub>Measurement</sub> needed = 1 / risetime for ~5% error. (1ns risetime = 1GHz). Remember, BW<sub>Measurement</sub> is often limited by BW<sub>Accessories</sub>!

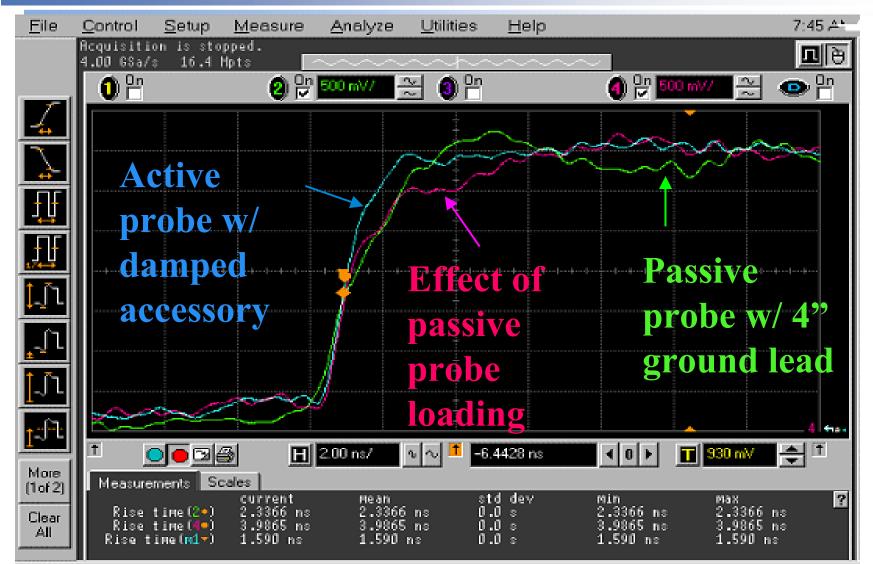

#### **Consider Probe Loading**

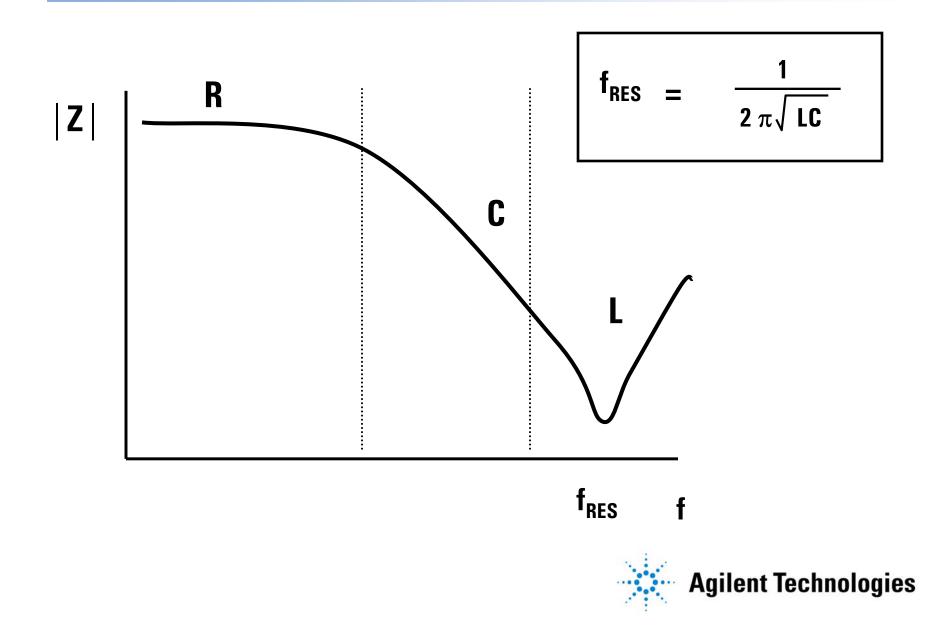

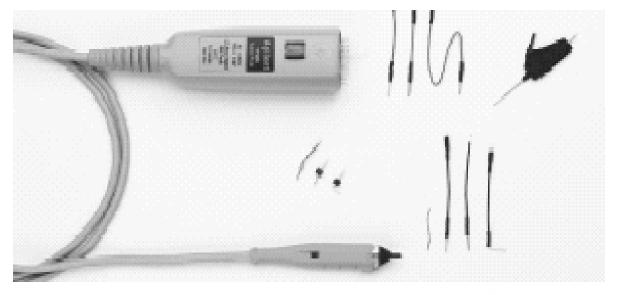

## Hint #8: Use 1nH/mm to Estimate f<sub>RES</sub>

1156A Active Probe w/5cm signal lead Input C = 0.8pF L = 50nH f<sub>RES</sub> = ~850MHz

1165A Passive Probe w/10cm ground lead Input C = 9pF L = 100nH f<sub>RES</sub> = ~167MHz

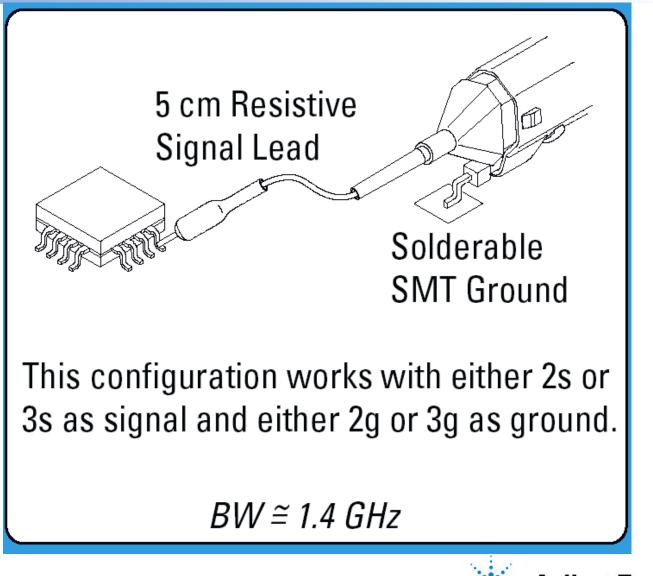

#### **1156A Recommended Configurations**

# Hint #9: Check Loading with 2 Probes

Agilent Technologies

- Hint #10: Always probe clocks at receiver.

- Hint #11: Probe LVDS clocks differentially (Zero crossing most important).

- Hint #12: Trigger on slowest clock when looking at divided clocks.

- Hint #13: Clock Layout: Avoid vias, split ground and power planes, and sharp corners. Layout power first, clocks next, then everything else.

- Hint #14: Recheck clocks after everything is turned on. May uncover data dependant coupling!

#### **Next Challenge - The Memory System**

#### Hint #15: Start off checking for Refresh.

|                                        | Pattern/State Trigger Setup                                                                             |

|----------------------------------------|---------------------------------------------------------------------------------------------------------|

| Command                                | Reset Pattern  Close    1  0  ×    Help  ▶?                                                             |

| No Operation (NOP)<br>Active (ACT)     | 2 3 4 D15 D14 D13 D12 D11 D10 D8 D8 D1 D6 D5 D4 D2 D1 6<br><b>SXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX</b> |

| Read (RD)                              | Pattern in Hex \$XX2 Thresholds                                                                         |

| Write (WR)                             | Digital Bus Pattern<br>Bus 1 Pattern in Hex X2                                                          |

| Burst Terminate (BT<br>Precharge (PCH) | Bus 2 Pattern in Hex 🔀                                                                                  |

| Autorefresh (ARF)                      |                                                                                                         |

| Load Mode Register (L.                 |                                                                                                         |

#### Hint #16: Isolate a Single Cycle

- Use special firmware or HDL to generate a continuous stream of just writes, then just reads.

- Vary data: All 1's, all 0's, checkerboards, to get more transistions.

- Look for illegal logic levels, setup/hold violations.

Check direction control on buffers.

- Check many address and data lines. Note worst ones (timing and signal integrity) for future work.

# Hint #17: Probe the Right End

Probe address and data writes at memory.

- Probe data reads at controller.

- Probe clocks at memory.

# Hint #18: Pattern Trigger Isolates Cycles

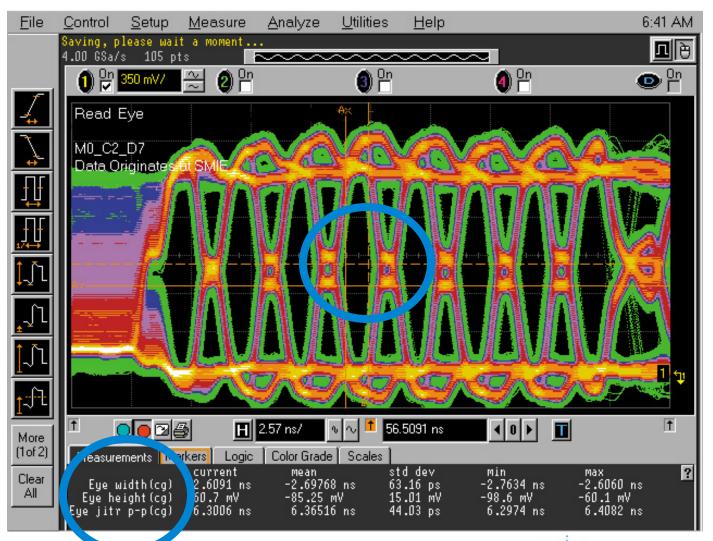

#### **DDR SDRAM Burst Read Example**

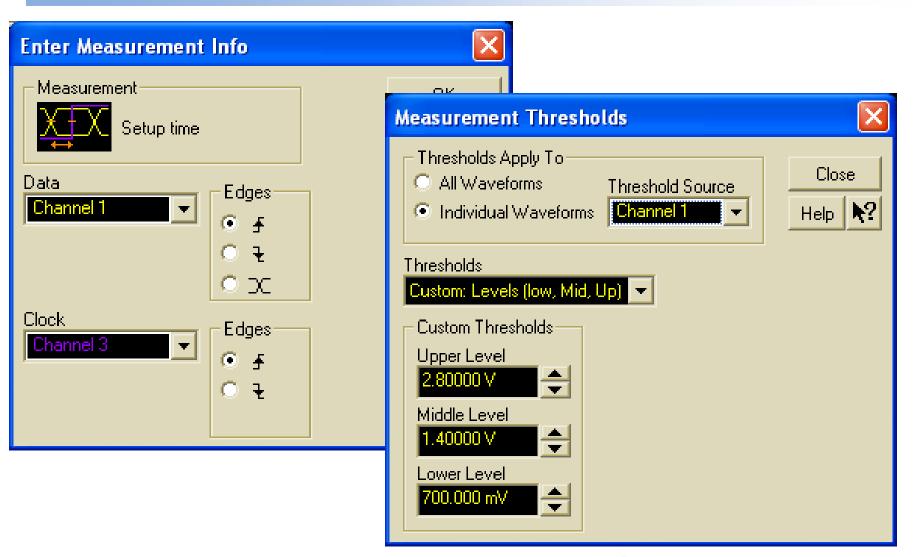

#### Hint #19: Use Custom Thresholds

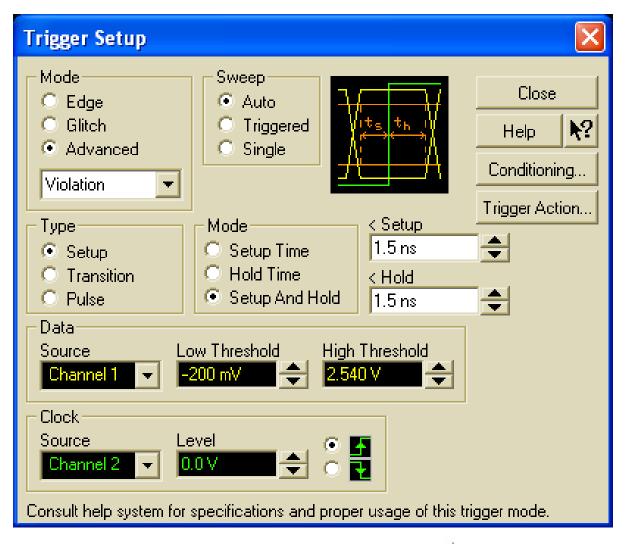

## Hint #20: Use Violation Triggering

#### Hint #21: Read the Fine Print

- Some vendors specify minimum risetime.

- Some specifications are functions of risetime.

- Some vendors specify N refreshes before use.

- Look for clock output R. Series terminate clocks with R<sub>term</sub> = R<sub>line</sub> - R<sub>source</sub>.

- Vary temperature if margin is small. Specs are tighter than they used to be!

- Verify revision of specification = revision of silicon.

#### Hint #22: Recheck Clocks and Refresh

- After system is up and running recheck clock signal integrity and worse case setup/hold lines. Look for data dependant problems.

- Also check refresh cycles. Sometimes controllers refresh fine with little memory activity but can leave out refresh as memory traffic increases.

#### **PCI Bus turn on hints**

- Again, clocks are most critical. Clocks are point to point - series terminated.

- Hint #23: Give clock traces more space even if you have to squeeze AD and control.

- Hint #24: Length dictates speed (33MHz or 66MHz) and minimizes timing margin. Do not approach length limits unless absolutely necessary.

#### **Pause for Q&A**

- Trends in Embedded Systems

- SDRAM and PCI Overview

- Turn on Process Recommendations

- "Late in the Game" Debug Process Recommendations

- Recommended Agilent Products

- Additional References

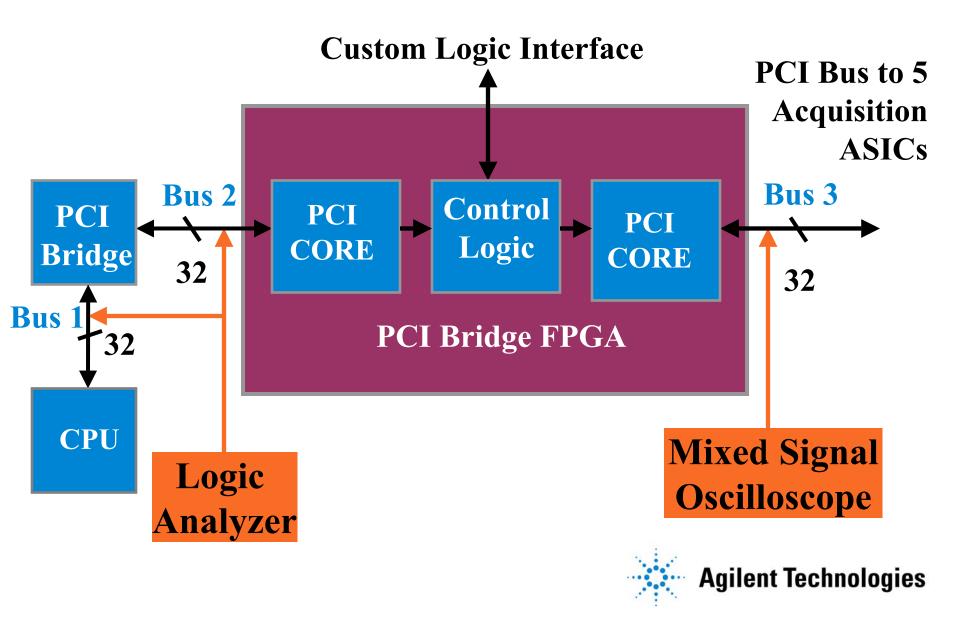

## **Example: PCI Bus Intermittent Lockup**

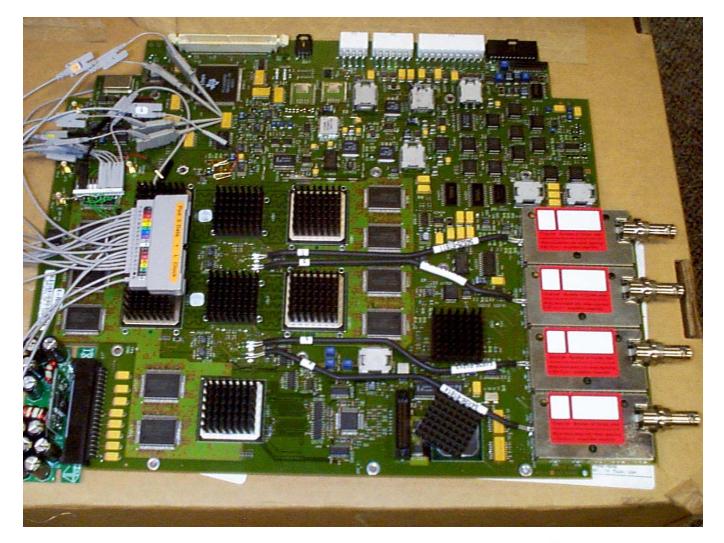

#### **Acquisition Board of 54832D**

Has 125MHz SDRAM for memory and 33MHz PCI bus for communication between ASICs and Host PC.

SDRAM worked fine. PCI bus had problems that threatened to delay shipments.

Team did not plan ahead no logic analyzer connectors for PCI bus on acquisition board.

Agilent Technologies

#### **Situation & Challenges**

- The problem happened very occasionally, and only on a few units.

- They had no idea where the write was going astray.

- They could easily hook up to Bus 1 (Backplane) and with some effort hook up to Bus 2 (Ribbon Cable), but found it nearly impossible to hook up to Bus 3 (SMT to BGA routing).

#### Hint #23: Break It Before You Fix It

- Look for units that fail most often.

- Modify firmware/HDL to fail more often.

- Vary temperature to fail more often.

- Duplicate failure in simulation.

#### Hint #24: Functional or Parametric?

| Functional    | Either      | Parametric    |

|---------------|-------------|---------------|

| Duplicates in | Caused by   | Observed with |

| Simulation    | Temperature | Scope         |

Observed with Varies with Logic Analyzer Code or HDL or Debugger

> Follows Board or Chip

#### **Debug Environment**

### **Logic Analyzer Isolates Fault**

| 1.       | le Window                             |                       | ons Invas        | smi Source     | ,<br>1              |                |                         | Hel                   |

|----------|---------------------------------------|-----------------------|------------------|----------------|---------------------|----------------|-------------------------|-----------------------|

|          | Time<br>Relative                      | Command<br>Text       | Address_L<br>Hex | Data_L<br>Text | Termination<br>Text | Latency<br>Hex | Efficiency %<br>Decimal | Mbytes/sec<br>Decimal |

|          | 88.000 ns                             |                       | 00000CF8         | 80003B08       | Initiator           | 03             | 025                     | 0045                  |

|          | 1.176 us<br>176.000 ns<br>2.792 us    | Cfg Read<br>I/O Write | 00040308         | ******01       | Initiator           | 06             | 014                     | 0005                  |

|          | 88.000 ns                             | 1/0 0/108             | 00000CF8         | 80003B40       | Initiator           | 03             | 025                     | 0045                  |

|          | 1.176 us<br>176.000 ns<br>3.600 us    | Cfg Read<br>I/O Write | 00040340         | xxxx8001       | Initiator           | 05             | 016                     | 0011                  |

| 2        | 240.000 us<br>240.000 ns<br>90.808 us |                       | 00008005         | xxxx20xx       | Initiator           | 08             | 011                     | 0004                  |

| <b>-</b> | 24.000 ns                             | 0000 090              | 00120002         | 00120002       |                     | 08             |                         |                       |

|          | 96.000 ns                             |                       |                  |                | Mstr Abort          | 06             | 016                     | 0000                  |

|          | 1.751 s<br>3.096 us<br>88.000 ns      | Mem Read<br>Mem Read  | FFFFFF0          | F526FF2E       | Initiator           |                | 000                     | 0001                  |

|          | 3.088 us<br>88.000 ns                 | Mem Read              | FFFFFFF4         | 00C01BFF       | Initiator           |                | 000                     | 0001                  |

|          | 3.096 us<br>88.000 ns                 | Mem Read              | FFFFFF8          | 00C01DEA       | Initiator           | 65             | 000                     | 0001                  |

|          | 3.088 us<br>96.000 ns                 | Mem Read              | FFFFFFC          | FC0000F0       | Initiator           | 65             | 000                     | 0001                  |

|          | 3.088 us                              | Mem Read              | FFFFFEO          | 00000000       | Initiator           |                | 000                     | 0001                  |

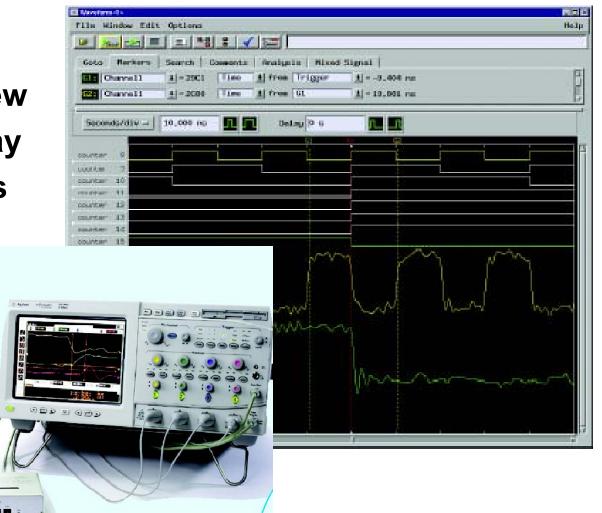

#### **MSO Finds Root Cause**

Analog channels see isolated clock coupling

Digital channels provide state trigger on first address phase after a bus turnaround

**Agilent Technologies**

- Trends in Embedded Systems

- SDRAM and PCI Overview

- Turn on Process Recommendations

- "Late in the Game" Debug Process Recommendations

- Recommended Agilent Products

- Additional References

# 34401A 6 1/2 Digit DMM

- \$1,163

- Accurate

- Fast

- Easy to Read

- Reliable

For more information on the 33401 Digital Multimeter, and other low-cost benchtop instruments,

visit www.agilent.com/find/everydaytools

#### **1156A 1.5GHz Active Probe**

- \$1,866

- Damped Accessories for Minimized Loading

- Small Size

- Documented BW for Recommended Accessories

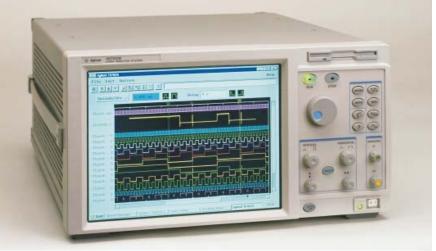

# **Agilent Infiniium MSOs**

- \$17K \$25K

- 600MHz and 1GHz

- 2+16 and 4+16 channel models

- MegaZoom Deep Memory

- 2M/channel Standard

- 8M/channel Optional

- http://www.agilent.com/ find/mso

# **Agilent Logic Analyzer Family**

- Modular, Standalone and PC Hosted models

- Wide variety of speed and channel count configurations

- Wide variety of probing solutions

- http://www.agilent.com/ find/logic

**Agilent Technologies**

# **E5850A Time Correlation Fixture**

- Automatic Deskew

- Combined Display

- Tracking Markers

ALLING S

- Trends in Embedded Systems

- SDRAM and PCI Overview

- Turn on Process Recommendations

- "Late in the Game" Debug Process Recommendations

- Recommended Agilent Products

- Additional References

## **Recommended App Notes**

- Debugging a PCI Bus with a Mixed-Signal Oscilloscope - Pub # 5988-7745EN

- Customer Validates Signal Integrity on 100 MHz DDR SDRAM With Mixed-Signal Oscilloscope - Pub # 5988-9265EN

- The Truth About the Fidelity of High-Bandwidth Voltage Probes - Pub # 5988-6515EN

- http://www.measurement.tm.agilent.com/n ew/category704.html

- Johnson, Howard W., High Speed Digital Design: A Handbook of Black Magic, Prentice Hall, 1993

- Witte, Robert A., *Electronic Test Instruments,* Prentice Hall, 1993

- Ganssle, Jack, The Art of Designing Embedded Systems, Newnes, 2000

#### **Thank You For Attending**

# Debug Your Embedded System More Quickly